# V-Band High-Efficiency High-Power AlInAs/GaInAs/InP HEMT's

Mehran Matloubian, Linda M. Jelloian, April S. Brown, Loi D. Nguyen, Lawrence E. Larson, M. J. Delaney, Mark A. Thompson, R. A. Rhodes, and J. E. Pence

**Abstract**—In this paper, we report on the state-of-the-art power performance of InP-based HEMT's at V-band. Power HEMT's were fabricated using two different material layer structures. The power performances of these HEMT's were measured at 59 GHz. We were able to achieve an output power of 155 mW with 4.9 dB gain, and power-added efficiency of 30 percent from a 448- $\mu$ m-wide HEMT fabricated on a  $\delta$ -doped channel layer structure. By using a double-doped layer structure, we were able to achieve an output power of 145 mW with 4.2 dB gain, and power-added efficiency of 24 percent. Output power of 288 mW with 3.6 dB gain and power-added efficiency of 20.4 percent were obtained by power combining two of the  $\delta$ -doped channel HEMT's. These combinations of output power and efficiency are the best reported to date for InP-based HEMT's, and are comparable to the best results reported for AlGaAs/InGaAs on GaAs pseudomorphic HEMT's at this frequency.

## I. INTRODUCTION

INP-BASED HEMT's have demonstrated record low-noise performance at V-band [1], [2]. But little work has been done on InP-based HEMT's for power applications due to the low gate-to-drain breakdown voltage and low Schottky barrier height of these HEMT's. At V-band, the highest output power previously reported for a single AlInAs/GaInAs/InP HEMT has been 26 mW with power-added efficiency of 33 percent [3]. So far, the most promising results have been obtained on pseudomorphic AlGaAs/InGaAs on GaAs HEMT's [4]–[6]. InP-based HEMT's offer a number of advantages over GaAs-based HEMT's for power applications. The thermal conductivity of InP is 40 percent higher than GaAs, allowing a lower operating channel temperature for the same power dissipation. Due to the larger conduction band discontinuity between  $\text{Al}_{0.48}\text{In}_{0.52}\text{As}$  and  $\text{Ga}_{0.47}\text{In}_{0.53}\text{As}$ , higher electron densities can be achieved in AlInAs/GaInAs/InP HEMT's than in AlGaAs/InGaAs/GaAs HEMT's. Coupled with the higher electron velocity in the channel, higher current densities can be achieved.

We previously reported that by proper device layer design, it is possible to overcome the drawbacks of InP-based HEMT's for power applications, and achieve power

Manuscript received March 26, 1993; revised June 18, 1993.

M. Matloubian, L. M. Jelloian, A. S. Brown, L. D. Nguyen, L. E. Larson, M. J. Delaney, and M. A. Thompson are with the Hughes Research Laboratories, Malibu, CA 90265.

R. A. Rhodes and J. E. Pence are with the Hughes Space and Communications Sector, El Segundo, CA 90245.

IEEE Log Number 9213004.

densities as high as 1 W/mm, and power-added efficiencies as high as 59 percent at 12 GHz [7]. In this paper, we report on the power performance of  $\delta$ -doped channel and double-doped AlInAs/GaInAs on InP HEMT's. Using these layer structures, we have achieved state-of-the-art power performance at 59 GHz. The results are comparable to the best reported performance for AlGaAs/InGaAs on GaAs pseudomorphic HEMT's at this frequency.

## II. DEVICE STRUCTURE

To achieve high current densities in power HEMT's without sacrificing the gate-to-drain breakdown voltage, several possible material layer structures can be used. In this study, we fabricated HEMT's using two different layer structures—a  $\delta$ -doped channel layer structure and a double-doped layer structure. In a  $\delta$ -doped channel layer structure (shown in Fig. 1), a plane of Si atoms is inserted at the center of the channel. In a double-doped layer structure (shown in Fig. 2), the channel is undoped and an additional donor layer is added below the channel. Both of these layers were grown by MBE on a semi-insulating InP substrate. The  $\delta$ -doped layer structure consisted of a 2500 Å AlInAs buffer layer followed by a 300 Å GaInAs channel. A plane of Si atoms, with a concentration of  $1.5 \times 10^{12} \text{ cm}^{-2}$ , was inserted at the center of this channel. In addition, a 50 Å AlInAs layer doped  $6 \times 10^{18} \text{ cm}^{-3}$ , separated by a 15 Å undoped AlInAs spacer layer, was grown on top of the channel. To improve the Schottky barrier height of the gate, and the gate-to-drain breakdown voltage, a 250 Å undoped layer of  $\text{Al}_{0.60}\text{In}_{0.40}\text{As}$  was then grown [8]. Finally, a 70 Å doped layer of GaInAs layer was grown to facilitate ohmic contact formation. The material had an electron sheet charge density of  $4.2 \times 10^{12} \text{ cm}^{-2}$  with a mobility of  $8500 \text{ cm}^2/\text{V}\cdot\text{s}$ . Even though doping the channel reduces the mobility of the electrons in the channel, it is significantly higher than the electron mobility of GaAs pseudomorphic HEMT's.

The double-doped layer structure had a  $\delta$ -doped layer below the GaInAs channel with a concentration of  $2.0 \times 10^{12} \text{ cm}^{-2}$  separated from the channel with a spacer layer thickness of 50 Å. The spacer layer was grown at significantly reduced temperatures (300–350°C) to prevent silicon movement into the channel [9]. The GaInAs channel was 200 Å thick. An additional donor layer consisting of

|                                             |                 |               |

|---------------------------------------------|-----------------|---------------|

| <b>Ga<sub>0.47</sub>In<sub>0.53</sub>As</b> | <b>CAP</b>      | <b>70 Å</b>   |

| <b>Al<sub>0.60</sub>In<sub>0.40</sub>As</b> | <b>SCHOTTKY</b> | <b>250 Å</b>  |

| <b>Al<sub>0.48</sub>In<sub>0.52</sub>As</b> | <b>Si DOPED</b> | <b>50 Å</b>   |

| <b>Al<sub>0.48</sub>In<sub>0.52</sub>As</b> | <b>SPACER</b>   | <b>15 Å</b>   |

| <b>Ga<sub>0.47</sub>In<sub>0.53</sub>As</b> | <b>CHANNEL</b>  | <b>150 Å</b>  |

| <hr/>                                       |                 |               |

| <b>Ga<sub>0.47</sub>In<sub>0.53</sub>As</b> | <b>CHANNEL</b>  | <b>150 Å</b>  |

| <hr/>                                       |                 |               |

| <b>Al<sub>0.48</sub>In<sub>0.52</sub>As</b> | <b>BUFFER</b>   | <b>2500 Å</b> |

| <hr/>                                       |                 |               |

| <b>InP SUBSTRATE</b>                        |                 |               |

| <hr/>                                       |                 |               |

| <b>Ga<sub>0.47</sub>In<sub>0.53</sub>As</b> | <b>CAP</b>      | <b>70 Å</b>   |

| <b>Al<sub>0.48</sub>In<sub>0.52</sub>As</b> | <b>SCHOTTKY</b> | <b>100 Å</b>  |

| <b>Al<sub>0.60</sub>In<sub>0.40</sub>As</b> | <b>SCHOTTKY</b> | <b>200 Å</b>  |

| <b>Al<sub>0.48</sub>In<sub>0.52</sub>As</b> | <b>Si DOPED</b> | <b>50 Å</b>   |

| <b>Al<sub>0.48</sub>In<sub>0.52</sub>As</b> | <b>SPACER</b>   | <b>15 Å</b>   |

| <b>Ga<sub>0.47</sub>In<sub>0.53</sub>As</b> | <b>CHANNEL</b>  | <b>200 Å</b>  |

| <b>Al<sub>0.48</sub>In<sub>0.52</sub>As</b> | <b>SPACER</b>   | <b>50 Å</b>   |

| <hr/>                                       |                 |               |

| <b>Al<sub>0.48</sub>In<sub>0.52</sub>As</b> | <b>BUFFER</b>   | <b>2500 Å</b> |

| <hr/>                                       |                 |               |

| <b>InP SUBSTRATE</b>                        |                 |               |

Fig. 1. Cross section of the  $\delta$ -doped channel AlInAs/GaInAs on InP power HEMT.

SI  $\delta$ -DOPED LAYER

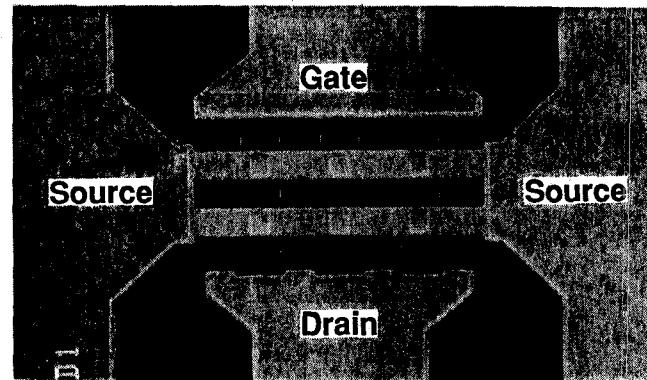

Fig. 3. SEM of  $0.15 \mu\text{m} \times 448 \mu\text{m}$  InP-based power HEMT.

(wafer B). The HEMT's had a unit gate-finger width of  $56 \mu\text{m}$  and a total gate width of  $448 \mu\text{m}$  with a gate-to-gate spacing of  $20 \mu\text{m}$ . The picture of the device is shown in Fig. 3. The completed wafers were thinned to a thickness of  $50 \mu\text{m}$ , and source vias were etched using a wet-etch process. The vias were approximately  $75 \mu\text{m}$  in diameter on the back of the wafer, and  $25 \mu\text{m}$  in diameter at the source pads. The back of the wafer was then metallized and plated with  $8 \mu\text{m}$  of gold to add support to the wafer.

### III. DEVICE PERFORMANCE

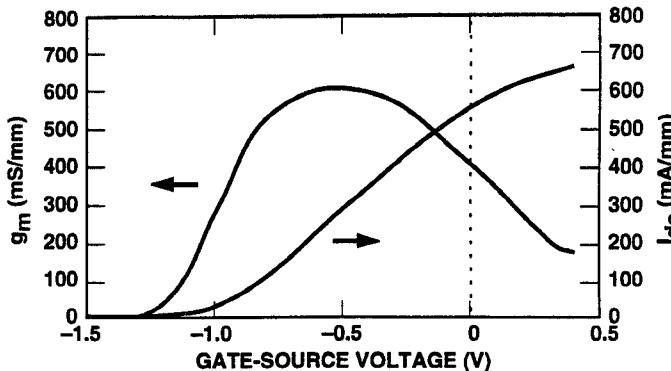

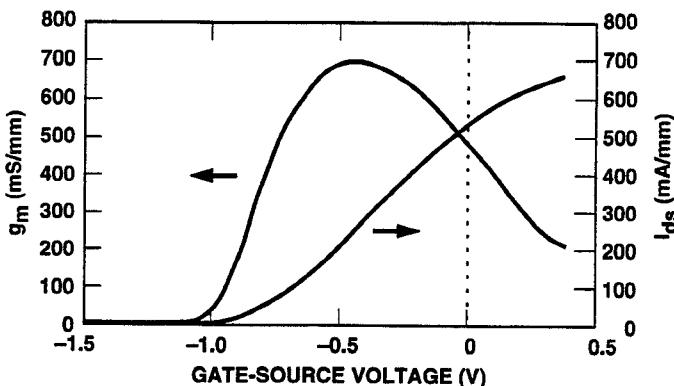

A plot of transconductance and drain current versus gate-to-source voltage for wafer A is shown in Fig. 4. The device has a peak transconductance of  $600 \text{ mS/mm}$  at a drain-to-source voltage of  $1.5 \text{ V}$ . It has a full channel current of  $660 \text{ mA/mm}$  measured at a gate-to-source voltage of  $0.4 \text{ V}$  and  $I_{dss}$  of  $550 \text{ mA/mm}$ . The gate-to-drain breakdown voltage measured at  $1 \text{ mA/mm}$  of gate current was  $7 \text{ V}$  with a gate-to-drain turn-on voltage of  $0.65 \text{ V}$ . The  $448 \mu\text{m}$  HEMT's from wafer A had a current gain cutoff frequency ( $f_T$ ) of  $140 \text{ GHz}$  at a  $V_{ds}$  of  $1.5 \text{ V}$ . For wafer B, the plot of transconductance and drain current is shown in Fig. 5. In this case, the device has a peak transconductance of  $700 \text{ mS/mm}$ . The full channel current is  $660 \text{ mA/mm}$  with  $I_{dss}$  of  $530 \text{ mA/mm}$ . The gate-to-drain breakdown voltage for wafer B was  $6.5 \text{ V}$  with a gate-to-drain turn-on voltage of  $0.75 \text{ V}$ . The typical  $f_T$  of  $448 \mu\text{m}$ -wide HEMT's from wafer B was  $120 \text{ GHz}$ . Both of these wafers had a transconductance of more than  $300 \text{ mS/mm}$  over a drain current range of approximately  $35\text{--}605 \text{ mA/mm}$ . A summary of the dc characteristics of the two wafers is shown in Table I.

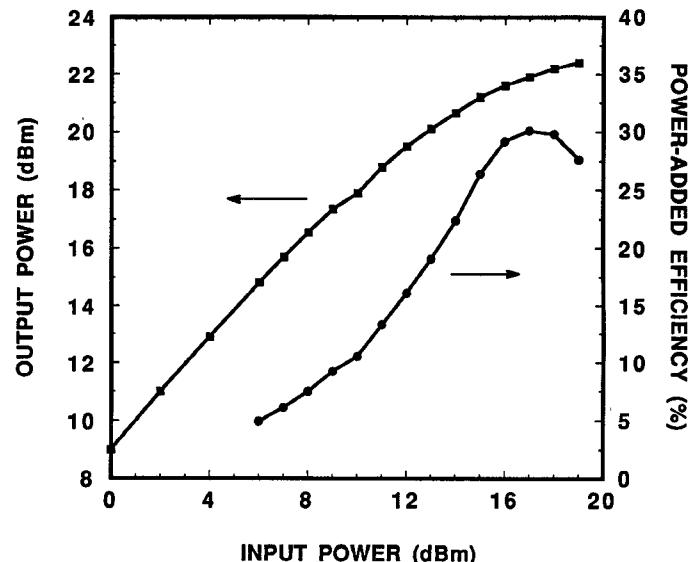

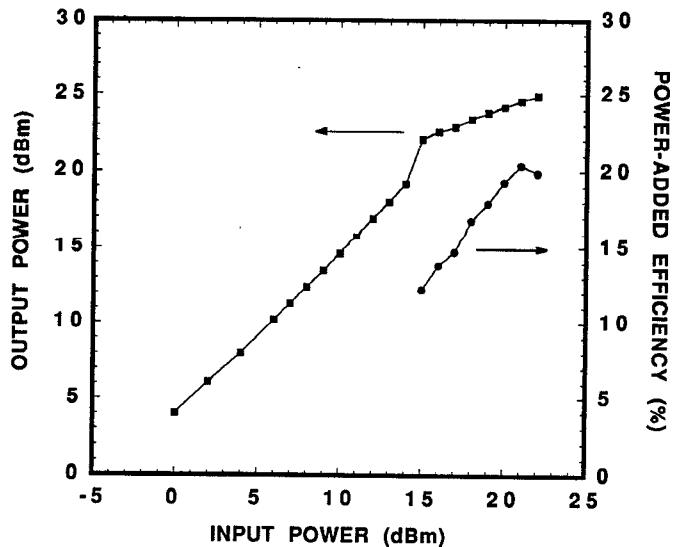

To measure the performance of the power HEMT's at  $59 \text{ GHz}$ , the devices from both wafers A and B were mounted in RF test fixtures with finline waveguide-to-microstrip transitions. The waveguide fixtures had a total loss of approximately  $1.2 \text{ dB}$  at  $59 \text{ GHz}$ , and the power measurements were corrected for this loss. The power characteristics of a  $448\text{-}\mu\text{m}$ -wide HEMT from wafer A is shown in Fig. 6. The transistor was biased at a drain-to-source voltage of  $3.5 \text{ V}$ . The device has a maximum power-added efficiency of  $30 \text{ percent}$ , with an output

$50 \text{ \AA}$  of silicon doped layer ( $6.5 \times 10^{18} \text{ cm}^{-3}$ ) separated by a  $15 \text{ \AA}$  spacer layer was grown on top of the channel. The Schottky layer consisted of  $200 \text{ \AA}$  of undoped  $\text{Al}_{0.60}\text{In}_{0.40}\text{As}$  followed by  $100 \text{ \AA}$  of undoped  $\text{Al}_{0.48}\text{In}_{0.52}\text{As}$ , and a  $70 \text{ \AA}$   $\text{Ga}_{0.47}\text{In}_{0.53}\text{As}$  layer was used as the cap. The double-doped layer structure had a sheet charge density of  $4.3 \times 10^{12} \text{ cm}^{-2}$  with a mobility of  $9800 \text{ cm}^2/\text{V}\cdot\text{s}$ . In both of these layer structures, electron sheet charge density in the channel is increased without increasing the doping in the top donor layer, which would result in the reduction of the gate-to-drain breakdown voltage.

HEMT's were fabricated on these two layer structures using a planar process. Source and drain ohmic contacts were formed using  $\text{AuGe}/\text{Ni}/\text{Au}$  alloy with drain-to-source spacing of  $2 \mu\text{m}$ . Boron ion implantation was used for device isolation. The gates with a T-shaped cross section were formed by  $\text{Ti}/\text{Pt}/\text{Au}$  metallization with a gate length of  $0.15 \mu\text{m}$  on the  $\delta$ -doped channel wafer (wafer A) and a gate length of  $0.2 \mu\text{m}$  on the double-doped wafer

TABLE I

SUMMARY OF THE DC CHARACTERISTICS OF THE  $\delta$ -DOPED CHANNEL AND THE DOUBLE-DOPED CHANNEL POWER HEMT'S

| Wafer Profile | $g_m$<br>(mS/mm) | $I_{df}$<br>(mA/mm) | $I_{dss}$<br>(mA/mm) | $BV_{gd}$<br>(V) | $V_{gd}$ (V)<br>(turn-on) | $V_{pinch-off}$<br>(V) |

|---------------|------------------|---------------------|----------------------|------------------|---------------------------|------------------------|

| delta-doped   | 600              | 660                 | 550                  | 7                | 0.65                      | -1.2                   |

| double-doped  | 700              | 660                 | 530                  | 6.5              | 0.75                      | -1                     |

Fig. 4. Plot of transconductance and drain current as a function of gate-to-source bias at  $V_{ds} = 1.5$  V for the  $\delta$ -doped channel wafer (wafer A).

Fig. 5. Plot of transconductance and drain current as a function of gate-to-source bias at  $V_{ds} = 1.5$  V for the double-doped wafer (wafer B).

power of 155 mW and 4.9 dB gain. The transistor has a linear gain of 8 dB and a saturated output power of more than 180 mW with a 3 dB gain. The 448- $\mu$ m-wide HEMT from wafer B was also biased at a drain-to-source voltage of 3.5 V. The device had a maximum power-added efficiency of 24 percent, with an output power of 145 mW and 4.2 dB gain. The linear gain for this device was approximately 7 dB. Table II shows a summary of the power performance of devices from these two wafers.

To achieve higher output powers at 59 GHz, branch-line couplers fabricated on alumina substrates were used to power combine two 448- $\mu$ m-wide HEMT's from wafer A. Fig. 7 shows the power characteristics of the two devices combined. The discontinuity in the output power is due to retuning of the amplifiers at that input power level. The output power at the maximum power-added efficiency of 20.4 percent is 288 mW with a gain of 3.6 dB. The combiner has an output power of more than 320 mW

Fig. 6. Power characteristics of a 448- $\mu$ m-wide  $\delta$ -doped channel HEMT at 59 GHz.

TABLE II

SUMMARY OF THE POWER PERFORMANCE OF THE  $\delta$ -DOPED CHANNEL AND THE DOUBLE-DOPED CHANNEL POWER HEMT'S

| Wafer        | Output Power<br>(mW) | Power-Added<br>Efficiency<br>(%) | Power Gain<br>(dB) | Linear Gain<br>(dB) |

|--------------|----------------------|----------------------------------|--------------------|---------------------|

| delta-doped  | 155                  | 30                               | 4.9                | 8                   |

| double-doped | 145                  | 24                               | 4.2                | 7                   |

Fig. 7. Power characteristics of power combined two 448- $\mu$ m-wide  $\delta$ -doped channel HEMT's at 59 GHz.

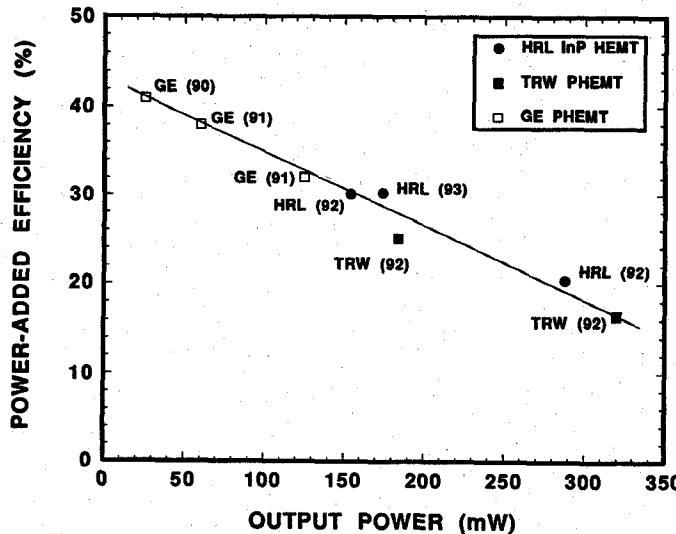

Fig. 8. Comparison of the-state-of-art power performance for HEMT's at about 60 GHz.

with power-added efficiency of 19 percent. A comparison of state-of-the-art power performance for HEMT's at 60 GHz is shown in Fig. 8. As can be seen from a comparison of output power and power-added efficiency, the data presented in this paper on AlInAs/GaInAs/InP HEMT's are comparable to the best results reported on AlGaAs/InGaAs/GaAs PHEMT's.

#### IV. CONCLUSION

In this paper, we compared two possible layer structures for fabrication of V-band power HEMT's and reported the first V-band power results of a double-doped AlInAs/GaInAs on InP HEMT. We were able to achieve an output power of 155 mW with power-added efficiency of 30 percent and 4.9 dB gain from a  $\delta$ -doped layer structure, and an output power of 145 mW with 4.2 dB gain and power-added efficiency of 24 percent from a double-doped layer structure. The lower gain and efficiency of the double-doped layer structure are believed to be due to the slightly longer gate length of the devices from that wafer. Using a gate length of 0.15  $\mu\text{m}$  with the double-doped layer structure should increase the gain, and therefore the power-added efficiency of the transistor. Recently, we have demonstrated device yield of more than 90 percent for 50- $\mu\text{m}$ -wide low-noise InP-based HEMT's with gate length of 0.1  $\mu\text{m}$  [10]. By further optimization of the material layer structure, and by incorporating a 0.1  $\mu\text{m}$  gate in our power HEMT's, we expect improvements in V-band power performance of the transistors.

#### REFERENCES

- [1] S. Vaughn, K. White, U. K. Mishra, M. J. Delaney, P. Greiling, and S. Rosenbaum, "High performance V-band low noise amplifiers," in *1989 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 801-804.

- [2] K. H. G. Duh, P. C. Chao, P. Ho, M. Y. Kao, P. M. Smith, J. M. Ballingall, and A. A. Jabra, "High performance InP-based HEMT millimeter-wave low-noise amplifiers," in *1989 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 805-808.

- [3] M.-Y. Kao, P. M. Smith, P. C. Chao, and P. Ho, "Millimeter wave performance of InAlAs/GaInAs/InP HEMT's," in *Proc. IEEE/Cornell Conf. Advance Concepts High Speed Semiconductor Devices Circuits*, pp. 469-477, 1991.

- [4] M.-Y. Kao, P. M. Smith, P. Ho, P. C. Chao, K. H. G. Duh, A. A. Jabra, and J. M. Ballingall, "Very high power-added efficiency and low-noise 0.15  $\mu\text{m}$  gate-length pseudomorphic HEMT's," *IEEE Electron Device Lett.*, vol. 10, pp. 580-582, Dec. 1989.

- [5] K. L. Tan, D. C. Streit, R. M. Dia, S. K. Wang, A. C. Han, P.-M. D. Chow, T. Q. Trinh, P. H. Liu, J. R. Velebir, and H. C. Yen, "High-power V-band pseudomorphic InGaAs HEMT," *IEEE Electron Device Lett.*, vol. 12, pp. 213-214, May 1991.

- [6] J. Goel, K. L. Tan, D. I. Stones, R. W. Chan, D. C. Streit, S. Peranton, and J. Schellenberg, "60 GHz power amplifier using PHEMT," in *1992 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 587-589.

- [7] M. Matloubian, L. D. Nguyen, A. S. Brown, L. E. Larson, M. A. Melendes, and M. A. Thompson, "High power and high efficiency AlInAs/GaInAs on InP HEMT's," in *1991 IEEE MTT-S Int. Microwave Symp. Dig.*, pp. 721-724.

- [8] C. L. Lin, P. Chu, A. L. Keilner, H. H. Weider, and E. A. Rezek, "Composition dependence of Au/In<sub>1-x</sub>Al<sub>x</sub>As Schottky barrier heights," *Appl. Phys. Lett.*, vol. 49, no. 23, pp. 1593-1595, Dec. 8, 1986.

- [9] A. S. Brown, L. D. Nguyen, R. A. Metzger, M. Matloubian, A. E. Schmitz, M. Lui, R. G. Wilson, and J. A. Henige, "Reduced silicon movement in GaInAs/AlInAs HEMT structures with low temperature AlInAs spacers," in *Proc. GaAs Related Compounds*, vol. 120, 1991, p. 281.

- [10] L. D. Nguyen, M. V. Le, M. J. Delaney, M. Lui, T. Liu, J. J. Brown, R. Rhodes, M. Thompson, and C. Hooper, "Manufacturability of 0.1  $\mu\text{m}$  millimeterwave low-noise InP HEMT's," in *1993 IEEE MTT-S Int. Microwave Symp. Dig.*

**Mehran Matloubian** received the M.S. degree in electrical engineering from University of California, at Los Angeles (UCLA), in 1985, and the Ph.D. degree in electrical engineering also from UCLA in 1989.

His academic research work was on microwave and millimeter-wave characterization of transistors and dielectric materials. He developed a picosecond optoelectronic system for measuring S-parameters of transistors and characterized HEMT's over a record bandwidth of 120 GHz. He joined the Hughes Research Laboratories in 1990. He is currently responsible for the development of InP-based HEMT's and circuits for microwave and millimeter-wave power applications. He has authored or coauthored over 20 papers and presentations.

**Linda M. Jelloian** received the B.S. degree (magna cum laude) in biology in 1982 and the M.A. degree in business administration in 1986, both from Pepperdine University, Malibu, CA.

Currently, she is pursuing the M.S. degree in electrical engineering at the California State University at Northridge. Since joining Hughes Research Laboratories, Malibu, CA, in 1982, she has made significant contributions to the process development and fabrication of ultrahigh-speed GaAs MESFET's, AlGaAs/GaAs HEMT's, and AlInAs/GaInAs HEMT's for low-noise and digital logic applications. Her work in this area has led to the successful demonstration of a 340-GHz  $f_T$  self-aligned-gate AlInAs/GaInAs HEMT and a 25-GHz AlInAs/GaInAs HEMT frequency divider. She is the author or coauthor of 20 publications and has one patent.

Ms. Jelloian is a member of the Alpha Chi Honor Society. She was a recipient of an Outstanding Science Department Graduate Award in 1982 and an Achievement Rewards for College Scientist for 1980 to 1982.

**April S. Brown** was born in Durham, NC, in 1960. She received the B.S.E.E. degree from North Carolina State University, Raleigh, 1981, and the M.S. degree in 1984 and the Ph.D. degree in 1985, both from Cornell University, Ithaca, NY, in electrophysics. Her thesis research concentrated on the growth of AlInAs and GaInAs by molecular-beam epitaxy.

During the academic year of 1985-1986, she taught at the University of Michigan, Ann Arbor, as an Assistant Professor. In 1986 she joined Hughes Research Laboratories, Malibu, CA, as a Member of the Technical Staff and was responsible for the pioneering development of InP-based HEMT materials and devices at Hughes. She temporarily left Hughes for the Army Research Office from 1988 to 1989, where she monitored programs in condensed matter physics. She rejoined Hughes in 1989. She is currently a Senior Scientist and is responsible for the growth and characterization of InP-based HEMT materials, the development of an InP-based power HEMT, as well as the exploration of novel materials and growth mechanisms.

Dr. Brown is a member of the APS.

**Lawrence E. Larson** was born in New York, NY, on November 17, 1957. He received the B.S. and M.Eng. degree from Cornell University, Ithaca, NY, in 1979 and 1980, and the Ph.D. degree from UCLA in 1986.

Since 1984 he has been with the Hughes Research Laboratories in Malibu, CA, where he is currently Head of the HEMT Technology Department in the Microwave Devices and Circuits Research Laboratory. He is also currently Assistant Program Manager to the Hughes MIMIC Program, and is an Adjunct Associate Professor of Electrical Engineering at UCLA. His current research areas are in the fields of III-V devices and circuits, the growth of III-V materials, and the applications of micromachining. He has authored or coauthored over 80 papers and presentations, and has received 12 patents.

**Mark A. Thompson** received the diploma in electrical engineering technology from Denver Institute of Technology, Denver, CO, in 1977.

He joined Hughes Research Laboratories in 1986. He has made significant contributions to the development and fabrication of ultrashort gate-length FET's and HEMT's. He is currently responsible for the electron-beam lithography system at Hughes, as well as the development and implementation of advanced electron-beam lithography processes. His work in this area has led to the successful fabrication of a submicron self-aligned-gate HEMT with a record  $f_T$  of over 340 GHz, the process for which he presently holds a patent. Prior to his employment with Hughes, he was with Texas Instruments. From 1977 to 1986 he performed failure analysis on MOS memories and contributed to the process and product development of advanced Schottky and advanced low power Schottky LSI and VLSI integrated circuits, programmable array logic circuits (PAL), and bipolar-complementary MOS (BiCMOS) integrated circuits. He has authored or contributed to over 15 publications in the fabrication of compound semiconductor devices and circuits.

**Loi D. Nguyen** was born in Saigon (now Ho Chi Minh City), Vietnam, in 1959. He received the A.S. degree (with high honors) in engineering science from Broome Community College, Binghamton, NY, in 1982, the B.S. degree (with distinction) in electrical engineering from Cornell University, Ithaca, NY, in 1984, and the Ph.D. degree in electrical engineering, also from Cornell University, in 1989. Through summer employment, he received additional training at IBM, Endicott, NY, 1983, IBM, Boca Raton, FL, 1984, and Honeywell Physical Sciences Center, Bloomington, MN, 1985-1988.

He has made significant contributions to the design, fabrication, and modeling of ultrashort gate-length High Electron Mobility Transistors (HEMT's). He is currently a Department Manager at Hughes Research Laboratories in Malibu, CA, and is responsible for the pilot line production of high-reliability, ultralow-noise InP-based HEMT's and their associated monolithic circuits for radars and satellite communications. His research interests concentrate on the design, fabrication, characterization, and modeling of ultrashort gate-length HEMT's, as well as the development of new and novel compound semiconductor materials and devices. He has written or contributed to approximately 30 publications.

**R. A. Rhodes**, photograph and biography not available at the time of publication.

**J. E. Pence**, photograph and biography not available at the time of publication.